Министерство высшего и среднего специального

образования РСФСР

Куйбышевский ордена Трудового Красного Знамени

авиационный институт имени академика С.П.Королева

МИКРОПРОЦЕССОРНЫЙ КОМПЛЕКТ

К 589

Утверждено

редакционно-издательским

советом института

в качестве методических

указаний для студентов

Куйбышев 1984

УДК 681.325

В методических указаниях по курсу "Цифровые вычислительные машины" приведено описание микропроцессорного комплекта К589, используемого при проектировании операционных устройств в качестве элементной базы; даны рекомендации по использованию основных элементов комплекта. Указания составлены на кафедре "Автоматизированные системы управления" и предназначены для студентов специальности 0646.

Составитель - В.Г. Иоффе

Рецензенты: канд.техн.наук доц. В.А.Глазунов,

канд.техн.наук доц. В.А.Лукиных

## Технические характеристики микропроцессорного набора К589

Серия К589 представляет собой комплект интегральных схем (ИС), состоящий из процессорной и интерфейсных схем. Комплект предназначен для построения быстродействующих контроллеров различной организации, микро- и мини-ЭВМ, систем обработки данных.

В состав серии входят следующие элементы:

- блок микропрограммного управления (БМУ) К589 ИКО1;

- центральный процессорный элемент (ЦПЭ) К589 ИКО2;

- схема ускоренного переноса (СУП) К589 ИКО3;

- многорежимный буферный регистр (МБР) К589 ИР12;

- блок приоритетного прерывания (БПП) К589 ИК14;

- шинный формирователь (ШФ) К589 АИ16;

- шинный формирователь с инверсией (ШФИ) К589 АИ26;

- многофункциональное синхронизирующее устройство (МСУ) К589 ХЛ4.

Микросхемы выполнены на основе ТТЛ с диодами шотки (ТТЛШ) и совместимы со всеми серийными ТТЛ схемами. Поэтому их применение не ограничивается рамками 589 серии. При проектировании цифровых систем элементы микропроцессорного набора К589 могут использоваться и в качестве автономных функциональных узлов.

При работе с серией К589 в качестве ЗУ микрокоманд рекомендуется использовать программируемое постоянное ЗУ К556 РТ4, К556РТ5 [1 - 3].

Схемы К589 рассчитаны на эксплуатацию в интервале рабочих температур от -10 до +70<sup>0</sup>С при напряжении питания - (+5 В ±5%). Остальные технические характеристики МИК589 приведены в табл. I.

Таблица I

| Обозначения<br>MC |      | Напряжение, В |        | Ток<br>потребле-<br>ния, мА | Средняя<br>мощность,<br>мВт | Длитель-<br>ность цикла<br>MC |

|-------------------|------|---------------|--------|-----------------------------|-----------------------------|-------------------------------|

|                   |      | п0            | п1     |                             |                             |                               |

| K589              | ИКО1 | < 0,5         | > 2,4  | < 240                       | 850                         | < 85                          |

| K589              | ИКО2 | < 0,5         | > 2,4  | < 190                       | 725                         | < 100                         |

| K589              | ИКО3 | < 0,5         | > 2,4  | < 130                       | 450                         | < 13                          |

| K589              | ИР12 | < 0,5         | > 3,65 | < 130                       | 450                         | < 35                          |

| K589              | ИК14 | < 0,5         | > 2,4  | < 130                       | 450                         | < 80                          |

| K589              | ХЛ4  | < 0,5         | 2,4    | < 95                        | 450                         | < 50                          |

| K589              | АП16 | < 0,7         | > 2,4  | < 130                       | 470                         | < 65                          |

| K589              | АП26 | < 0,7         | > 2,4  | < 130                       | 470                         | < 65                          |

## I. ЦЕНТРАЛЬНЫЙ ПРОЦЕССОРНЫЙ ЭЛЕМЕНТ (ЦПЭ)

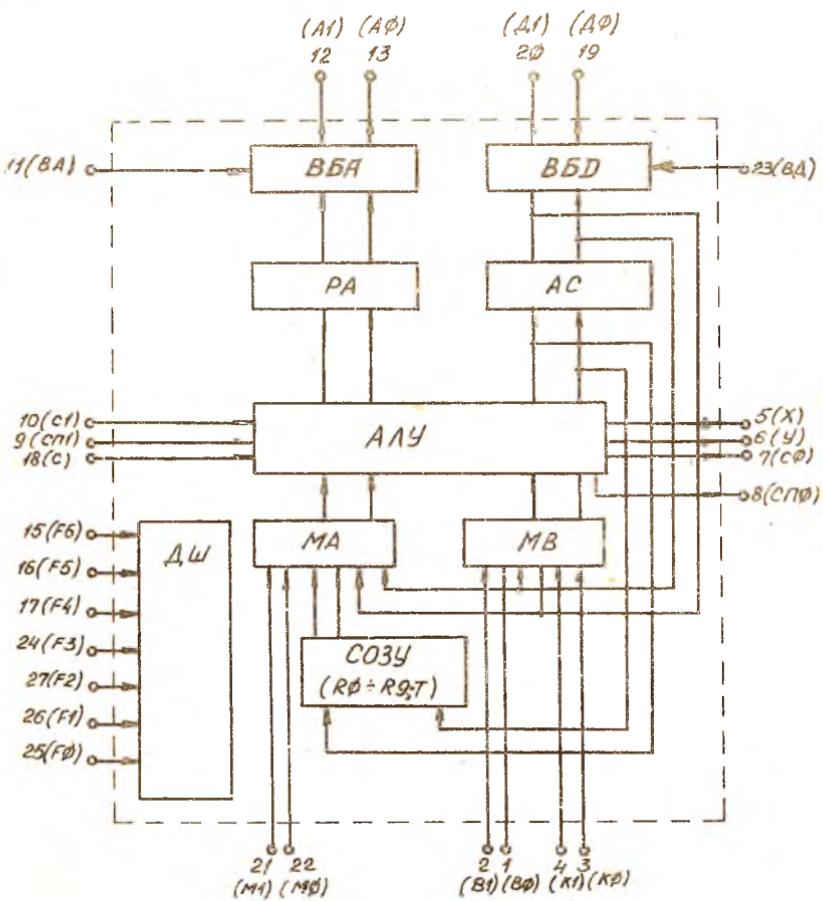

ЦПЭ, структурная схема которого представлена на рис. I, выполняет однотактные микрооперации над двухразрядными словами под действием микрокоманд, поступающих на шину ( $F_0 - F_8$ ). Для построения центрального процессора с длиной слова  $n$  необходимо соединить между собой  $n/2$  ЦПЭ.

Данные от внешних источников поступают в ЦПЭ по трем входнымшинам. Шина  $M$  предназначена для передачи данных из оперативной памяти, шина  $B$  — для приема данных от устройств ввода-вывода. Шина  $K$  служит для маскирования требуемых частей информационных слов, передаваемых по шине  $B$  или из аккумулятора  $AC$ . Маскирование позволяет ускорить анализ некоторых логических условий и приводит к экономии памяти микропрограмм [I].

Дополнительной функцией шин  $K$  является формирование констант, необходимых при выполнении микропрограмм. Возможность маскирования при помощи шины  $K$  значительно увеличивает функциональные возможности ЦПЭ.

В зависимости от особенностей организации вычислительной системы возможны и другие варианты использования шин  $M, B, K$ .

Данные, обработанные в ЦПЭ, передаются на внешние устройства по адресным шинам  $A$  и информационным выходным шинам  $D$ . Выходные

Рис. I

шины  $A$  и  $D$  реализованы на элементах с тремя состояниями ( $0, 1, \infty$ ), что упрощает организацию магистралей вычислительной системы. Управление состоянием шин  $A$  и  $D$  производится сигналами вход разрешения адреса (BA) и вход разрешения данных (BD), поступающими соответственно на выходные буферы VBA и VBD. Остальные входы и выходы используются при организации многоразрядного центрального процессора и обеспечивают распространение переносов ( $X$ ,  $Y$  — выходы ускоренного пе-

Рис. 2

в аккумуляторе АС. На вход АЛУ данные поступают через два внутренних мультиплексора МА и МВ.

Особенность мультиплексора МВ состоит в том, что его выходные сигналы всегда образованы как поразрядная конъюнкция кодов на шине  $K$  и на шине  $B$  или с выхода АС.

Содержание микроопераций задается кодом  $F0 - F6$ , состоящим из двух полей: поля функции  $F4 - F6$  ( $F$  - группа) и поля адреса регистра  $F0 - F3$  ( $R$  - группа). Кодирование этих групп приведено в табл. 3.

Выполнение микрооперации заканчивается по срезу синхроимпульса, которым результат заносится в один из внутренних регистров ЦПЭ. С приходом очередного синхроимпульса цикл выполнения микрооперации повторяется.

При внешнем управлении синхросигналом импульс, поступающий на вход "С" ЦПЭ, в требуемые моменты времени может быть заблокирован. Этот прием называется условной синхронизацией. Отсутствие синхроимпульса означает, что содержимое регистров ЦПЭ не изменяется, хотя под действием кода  $F0 - F6$  АЛУ выполняет требуе-

реноса, СО - выход переноса, СI - вход переноса), сдвиги (Сл0 - выход на три состояния для сдвига вправо, СII - вход для сдвига вправо), синхронизацию (С).

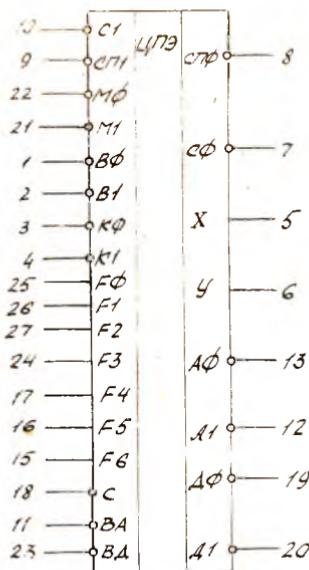

Условное обозначение ЦПЭ на электрических схемах показано на рис. 2, а назначения выводов даны в табл. 2.

С семиразрядной шиной  $F$  по фронту сигнала синхронизации код микрооперации через дешифратор дш преобразуется в систему совместимых управляющих сигналов для задания функций арифметико-логического устройства (АЛУ), выбора внутренних регистров и магистралей.

АЛУ может реализовать более 40 логических и арифметических микроопераций над операндами, находящимися на внешних шинах и внутренних регистрах ЦПЭ. Внутри ЦПЭ данные могут храниться в одиннадцати регистрах сверхоперативного запоминающего устройства (СОЗУ) ( $R0 - R9, T$ ) и.

Т а б л и ц а 2

| Контакт | Обозначение            | Наименование                | Тип выхода    | Примечание |

|---------|------------------------|-----------------------------|---------------|------------|

| I - 2   | <i>Bф...</i> <i>B1</i> | Входы внешней шины          |               |            |

| 3...4.  | <i>Kф...</i> <i>K1</i> | Входы маскирующей шины      |               |            |

| 5,6     | <i>X,Y</i>             | Выходы ускоренного переноса | два состояния |            |

| 7       | <i>Cф</i>              | Выход переноса              | Три состояния |            |

| 8       | <i>СПф</i>             | Выход сдвига вправо         | - " -         |            |

| 9       | <i>СП1</i>             | Вход для сдвига вправо      |               |            |

| 10      | <i>C1</i>              | Вход переноса               |               |            |

| 11      | <i>BA</i>              | Вход разрешения адреса      |               |            |

| I2...13 | <i>AI...</i> <i>Aф</i> | Выходы адреса памяти        | Три состояния |            |

| 14      |                        | Общий                       |               |            |

| I5...17 | <i>F6...</i> <i>F4</i> | Входы кода микро-команды    |               |            |

| 24...27 | <i>F3...</i> <i>Fф</i> |                             |               |            |

| 18      | <i>C</i>               | Вход синхронизации          |               |            |

| 19,20   | <i>Дф...</i> <i>Д1</i> | Выходы информации           | Три состояния |            |

| 21...22 | <i>M1...</i> <i>Mф</i> | Входы информации            |               |            |

| 23      | <i>ВД</i>              | Вход разрешения данных      |               |            |

| 28      |                        | Питание                     |               |            |

На выходах *X*, *Y*, *F6...* *F4* выходная и входная информация представлена в прямом коде, на остальных – в обратном, логической *н1* соответствует высокий уровень напряжения

мую микрооперацию. Это происходит потому, что АЛУ представляет собой комбинационную схему, для функционирования которой синхроимпульс не требуется.

Условная синхронизация экономит память за счет сокращения числа микрокоманд, необходимых для выполнения условных переходов, и увеличивает быстродействие [1,3].

Перечень микроопераций и их описание приведены в табл. 4, где: *M,B,K* – код числа на шинах *M,B,K* соответственно;

Таблица 3

| Группа функций<br>( $F$ - групп-<br>па) | $F6$ | $F5$ | $F4$ |

|-----------------------------------------|------|------|------|

| 0                                       | 0    | 0    | 0    |

| 1                                       | 0    | 0    | 1    |

| 2                                       | 0    | 1    | 0    |

| 3                                       | 0    | 1    | 1    |

| 4                                       | 1    | 0    | 0    |

| 5                                       | 1    | 0    | 1    |

| 6                                       | 1    | 1    | 0    |

| 7                                       | 1    | 1    | 1    |

- $C_I, C_{II}$  - значение переменных на входах цепи переноса и цепи сдвига вправо соответственно;

$C_0, C_{II_0}$  - значение переменных на выходах цепи переноса и цепи сдвига вправо;

$AC$  - содержимое аккумулятора;

$AT$  - содержимое  $AC$  или регистра  $T$  в зависимости от кода группы;

$R_n$  - содержимое регистра с номером  $n$ , в т.ч. и регистров  $AC$  и  $T$ . Номер регистра определяется кодом  $R$ -группы;

| Группа регистра<br>( $R$ - групп-<br>па) | Регистр | $F3$ | $F2$ | $F1$ | $F\phi$ |

|------------------------------------------|---------|------|------|------|---------|

| 1                                        | $R_0$   | 0    | 0    | 0    | 0       |

|                                          | $R_1$   | 0    | 0    | 0    | 1       |

|                                          | $R_2$   | 0    | 0    | 1    | 0       |

|                                          | $R_3$   | 0    | 0    | 1    | 1       |

|                                          | $R_4$   | 0    | 1    | 0    | 0       |

|                                          | $R_5$   | 0    | 1    | 0    | 1       |

|                                          | $R_6$   | 0    | 1    | 1    | 0       |

|                                          | $R_7$   | 0    | 1    | 1    | 1       |

| 2                                        | $R_8$   | 1    | 0    | 0    | 0       |

|                                          | $R_9$   | 1    | 0    | 0    | 1       |

|                                          | $T$     | 1    | 1    | 0    | 0       |

|                                          | $AC$    | 1    | 1    | 0    | 1       |

| 3                                        | $T$     | 1    | 0    | 1    | 0       |

|                                          | $AC$    | 1    | 1    | 1    | 1       |

Таблица 4

| № |   | Код                     |                                  | Содержание микропрограмм                     |                                   |                                                 |                                             |

|---|---|-------------------------|----------------------------------|----------------------------------------------|-----------------------------------|-------------------------------------------------|---------------------------------------------|

|   |   | микро-<br>операци-<br>и | номер<br>микро-<br>операци-<br>и | К = 00                                       | К = 11                            |                                                 |                                             |

| 1 | 2 | $\overline{3}$          | $\overline{4}$                   | ФУНКЦИЯ                                      | ФУНКЦИЯ                           | МНЕ-<br>СЛУЖИЩА<br>МОДУЛЯ<br>МИКРО-<br>ОПЕРАЦИИ | ПОД-<br>ПРО-<br>МЕЖДУ<br>МИКРО-<br>ОПЕРАЦИИ |

| 1 | 0 | $\overline{1}$          | $\overline{5}$                   | $R_n := R_n + C_1$                           | $R_n := R_n + C_1$                | $\overline{6}$                                  | $\overline{7}$                              |

| 2 | 3 | $\overline{1}$          | $\overline{6}$                   | $R_n := R_n + (AC \wedge K) + C_1$           | $R_n := R_n + C_1$                | $\overline{8}$                                  | $\overline{9}$                              |

| 3 | 2 | $\overline{1}$          | $\overline{7}$                   | $R_n := (AC \wedge K) + C_1 - 1$             | $R_n := C_1 - 1$                  | $\overline{10}$                                 | $\overline{11}$                             |

| 4 | 2 | $\overline{11}$         | $\overline{8}$                   | $AT := (AC \wedge K) + C_1 - 1$              | $AT := C_1 - 1$                   | $\overline{12}$                                 | $\overline{13}$                             |

| 5 | 1 | $\overline{1}$          | $\overline{9}$                   | $PA := K \vee R_n$<br>$R_n := R_n + K + C_1$ | $PA := R_n$<br>$R_n := R_n + C_1$ | $\overline{14}$                                 | $\overline{15}$                             |

| 6 | 3 | $\overline{11}$         | $\overline{10}$                  | $AT := AT + (B \wedge K) + C_1$              | $AT := AT + C_1$                  | $\overline{16}$                                 | $\overline{17}$                             |

| 7 | 2 | $\overline{11}$         | $\overline{11}$                  | $AT := (B \wedge K) + C_1 - 1$               | $AT := C_1 - 1$                   | $\overline{18}$                                 | $\overline{19}$                             |

| 8 | 3 | $\overline{11}$         | $\overline{12}$                  | $AT := M + (AC \wedge K) + C_1$              | $AT := M + C_1$                   | $\overline{20}$                                 | $\overline{21}$                             |

| 0 | 0 | $\overline{11}$         | $\overline{13}$                  |                                              |                                   | $\overline{22}$                                 | $\overline{23}$                             |

ПРОДОЛЖЕНИЕ ТЗОЛ. 4

Окончание табл. 4

| $\tau$ | $2$ | $3$             | $4$             | $5$             | $6$             | $7$             | $8$             | $C := C_1 \vee (AT \wedge B);$<br>$AT := AT \wedge (B \wedge K);$                     | $C := C_1;$<br>$AT := O;$  | $C := C_1;$<br>$AT := AT;$ | $C := C_1 \vee (AT \wedge B);$<br>$AT := AT \wedge B;$            | $C := C_1 \vee B;$<br>$AT := AT \wedge B;$ | $C := C_1 \vee (AT \wedge B);$<br>$AT := AT \wedge B;$            | $C := C_1 \vee (AT \wedge B);$<br>$AT := AT \wedge B;$            |

|--------|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------------------------------------------------------------------------------|----------------------------|----------------------------|-------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|

| 18     | 4   | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $C := C_1 \vee (AT \wedge B \wedge K);$<br>$AT := AT \wedge (B \wedge K);$            | $C := C_1;$<br>$AT := O;$  | $C := C_1;$<br>$AT := AT;$ | $C := C_1 \vee (AT \wedge B);$<br>$AT := AT \wedge B;$            | $C := C_1 \vee B;$<br>$AT := AT \wedge B;$ | $C := C_1 \vee (AT \wedge B);$<br>$AT := AT \wedge B;$            | $C := C_1 \vee (AT \wedge B);$<br>$AT := AT \wedge B;$            |

| 19     | 6   | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $C := C_1 \vee (B \wedge K);$<br>$AT := AT \wedge (B \wedge K);$                      | $C := C_1;$<br>$AT := AT;$ | $NOP$                      | $C := C_1 \vee B;$<br>$AT := AT \wedge B;$                        | $ORJ$                                      | $C := C_1 \vee (AT \wedge B);$<br>$AT := AT \wedge B;$            | $C := C_1 \vee (AT \wedge B);$<br>$AT := AT \wedge B;$            |

| 20     | 7   | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $C := C_1 \vee (AT \wedge B \wedge K);$<br>$AT := AT \oplus (B \wedge K);$            | $C := C_1;$<br>$AT := AT;$ | $CMA$                      | $C := C_1 \vee (AT \wedge B);$<br>$AT := AT \oplus B;$            | $XNZ$                                      | $C := C_1 \vee (AT \wedge B);$<br>$AT := AT \oplus B;$            | $C := C_1 \vee (AT \wedge B);$<br>$AT := AT \oplus B;$            |

| 21     | 4   | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $C := C_1 \vee (M \wedge AC \wedge K);$<br>$AT := O;$                                 | $C := C_1;$<br>$AT := O;$  | $C := C_1;$<br>$AT := O;$  | $C := C_1 \vee (M \wedge AC);$<br>$AT := M \wedge AC;$            | $ANM$                                      | $C := C_1 \vee (M \wedge AC);$<br>$AT := M \wedge AC;$            | $C := C_1 \vee (M \wedge AC);$<br>$AT := M \wedge AC;$            |

| 22     | 6   | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $C := C_1 \vee (AC \wedge K);$<br>$AT := M \vee (AC \wedge K);$                       | $C := C_1;$<br>$AT := M;$  | $DMF$                      | $C := C_1 \vee AC;$<br>$AT := M \vee AC;$                         | $Y$                                        | $C := C_1 \vee (M \wedge AC);$<br>$AT := M \wedge AC;$            | $C := C_1 \vee (M \wedge AC);$<br>$AT := M \wedge AC;$            |

| 23     | 7   | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $\overline{II}$ | $C := C_1 \vee (MA \wedge C \wedge K);$<br>$AT := M \overline{\oplus} (AC \wedge K);$ | $C := C_1;$<br>$AT := M;$  | $ACM$                      | $C := C_1 \vee (M \wedge AC);$<br>$AT := M \overline{\oplus} AC;$ | $XNM$                                      | $C := C_1 \vee (M \wedge AC);$<br>$AT := M \overline{\oplus} AC;$ | $C := C_1 \vee (M \wedge AC);$<br>$AT := M \overline{\oplus} AC;$ |

- := - знак присвоения;

РА - содержимое регистра адреса;

А, И, Л,: С, У - обозначение группы микроопераций (арифметические, пересылки, логические, сдвиги, управление соответственно);

ВН - подстрочный индекс, указывающий микрооперацию с внешними шинами М или В;

Л, П - подстрочные индексы, обозначающие принадлежность переменной левому (старшему) или правому (младшему) разряду ЦП.

П р и м е ч а н и я к т а б л . 4

1. Операция левого сдвига осуществляется, если при адресации  $R_n = AC$ .

2. При  $C_I = 0$  - хранение результата.

3. Установка  $R_n$  в нули ( $C_I = 1$ ) или единицы ( $C_I = 0$ ).

4. Одновременно с пересылкой содержимого  $R_n$  в РА возможно увеличение  $R_n$  на 1. Микрооперация используется для организации счетчика команд.

5. Загрузка РА единицами. Используется для установки в РА старшего адреса. Одновременно возможно уменьшение  $R_n$  на 1 ( $C_I = 0$ ). Вывчитание единицы осуществляется путем суммирования исходного кода с кодом "все единицы".

6. Установка АТ в нули ( $C_I = 1$ ) или единицы ( $C_I = 0$ ).

7. Поразрядная дизъюнкция значения нашине М с  $C_I$ . Используется при организации условного перехода. Например, проверка М на нуль. Если  $C_I = 0$ , то  $C_0 := 0$  при  $M = 0$ .

8. Содержимое АС или Т сдвигается вправо на один разряд; в старший (левый) разряд записывается значение  $C_{I-1}$ .

9. Используется для получения обратного ( $C_I = 0$ ) или дополнительного ( $C_I = 1$ ) кодов.

10. Применяется при организации условного перехода. При  $C_I = 0$  на  $C_0$  фиксируется значение  $(R_n \wedge AC)$ .

11. Проверка на ноль. Поразрядная дизъюнкция содержимого  $R_n$  с  $C_I$ . Если  $C_I = 0$ , то  $C_0 := 0$  при  $R_n = 0$ . При произвольном значении К можно проводить сравнение содержимого  $R_n$  и значения К.

12. Пустая микрооперация.

13. Логическое сложение и проверка на ноль содержимого АС перед сложением (см.п.10). Может использоваться при организации условных переходов.

14. Функция равнозначности (эквивалентности). Организация условного перехода на основании анализа  $(R_n \wedge AC)$ .

15. Проверка АТ на ноль и формирование признака результата в СО. Значение кода микрооперации см. в табл. 3.

Микрооперации (см.табл.4) разбиты на пять групп: с I по Ю позиции представлены, главным образом, арифметические микрооперации и пересылки (позиции I-5 отражают операции с внутренними регистрами, позиции 6,7 - с шинами В, позиции 8-9 - с шинами М).

Микрооперации сдвига выполняются путем подачи кода позиции II (правый сдвиг) и позиции I (левый сдвиг) при соответствующем значении К. С 12 по 23 позиции представлены логические микрооперации и микрооперации, с помощью которых можно организовать команды управления (условные переходы, обнуление регистров и занесение в них единичных значений и т.п.).

Аналогично предыдущему позиции (12-17) характеризуют микрооперации с внутренними регистрами (18-20) - с шинами В, (21-23) - с шинами М.

С помощью одного кода микрооперации в зависимости от значения К можно получать различные типы микроопераций. Например, с помощью кода позиции I получают II, A, C.

Особенности выполнения микроопераций следующие: информация с входных шин М, В может быть занесена только в регистры АС, Т, РА; результат микрооперации передается на выходные шины данных Д только с регистра АС, доступ на выходную шину адреса А возможен только из регистра РА.

## 2. БЛОК МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

Блок микропрограммного управления (БМУ) предназначен для реализации разнообразных управляющих функций, основные из которых: управление последовательностью выборки микрокоманд из памяти микропрограмм, хранение и проверка некоторых данных ЦПЭ, управление прерываниями микропрограммного уровня.

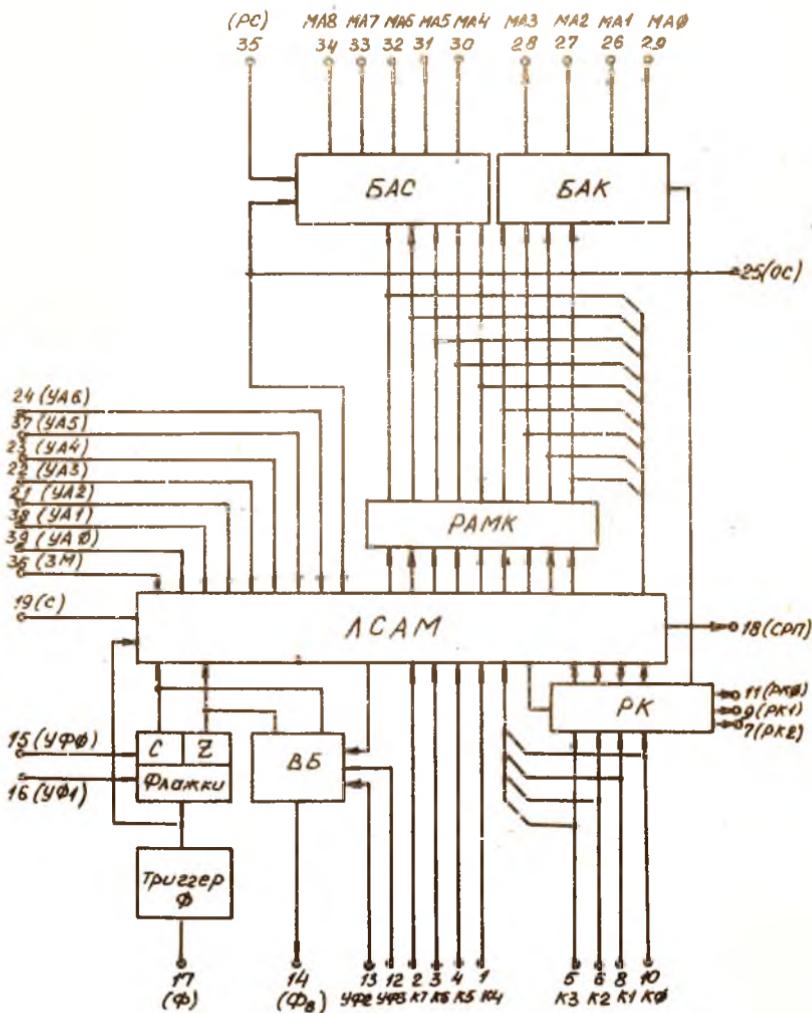

БМУ позволяет непосредственно адресоваться к 512 ячейкам памяти. При большем объеме ЗУ микропрограмм необходимо использовать страниценную адресацию, при которой объем страницы равен 512 ячейкам, а номер страницы указывается либо в микрокоманде, либо в специальном регистре. Структурную организацию БМУ иллюстрирует рис. 3, условные обозначения представлены по рис. 4. Назначение выводов БМУ показано в табл. 5.

Основой БМУ служит логическая схема определения следующего адреса микрокоманды (ЛСАМ). В общем случае этот адрес определяется:

Рис. 3

кодом команды (КО-К7), считываемой из оперативной памяти вычислительной системы;

кодом управления переходом к следующему адресу (УАО-УА6), находящемся в соответствующем поле микрокоманды;

кодом управления флаговой логики и содержащим триггеров  $F$ ,  $C$ ,  $Z$ . Загрузка триггеров осуществляется кодом УФ2, УФ3, а чтение записанной в них информации -- УФ0, УФ1; кодом текущего адреса микрокоманды;

значением кода на входе ЗМ.

Сформированный в ЛСАМ код загружается в регистр адреса микрокоманд (РАМК) и под действием сигнала общего строба (ОС) выдается на адресные линии (МА0-МА8) через выходные буферы адреса строки (БАС) и адреса колонки (БАК). БАС дополнительно управляет сигналом разрешения выдачи адреса строки -- РС. Данные на выходе БАС (МА4-МА8) кодируют номер одной из 32 строк матрицы памяти микрокоманд, а на выходе БАК (МА0-МА3) -- одной из 16 колонок. Матричная организация массива адресов упрощает логику формирования следующего адреса и приводит к минимизации количества выводов БМУ.

Кроме формирования адреса БМУ может выполнять следующие микрооперации:

прием начального адреса микрокоманд по шинам КО-К7. Данные с линий К4-К7 переносятся на разряды РАМК, соответствующие выходам колонок МА0-МА3, а с линий КО-К3 -- на разряды, соответствующие выходам строк МА4-МА7. Старший разряд РАМК устанавливается в нулевое состояние. При выполнении операции занесения начального адреса уровень сигнала на входе ЗМ должен соответствовать единичному значению;

хранение и анализ четырех разрядов кода команды (КО-К3) на регистре команд РК;

выдачу разрядов (КО-К2) в вычислительную систему для дальнейшего использования;

запоминание сигналов в триггерах  $C$  и  $Z$ , поступающих по линии  $\Phi$ , и условный переход по их значениям. В частном случае на вход  $\Phi$  могут поступать сигналы переноса и сдвига, возникающие при выполнении операций в ПЛЗ;

|    |     |                |    |

|----|-----|----------------|----|

| 36 | ЗМ  | БМУ            | 34 |

| 47 | УФ  | МА8            | 33 |

| 24 | УА6 | МА7            | 32 |

| 37 | УА5 |                |    |

| 23 | УА4 | МА6            | 31 |

| 22 | УА3 | МА5            | 30 |

| 21 | УА2 | МА4            | 29 |

| 38 | УА1 | МА3            | 28 |

| 39 | УА0 | МА2            | 27 |

| 12 | УФ3 | МА1            | 26 |

| 13 | УФ2 |                |    |

| 16 | УР1 | МА0            | 25 |

| 15 | УФ0 |                |    |

| 2  | КО7 |                |    |

| 3  | КО6 | РК2            | 2  |

| 4  | КО5 |                |    |

| 1  | КО4 | РК1            | 9  |

| 5  | КО3 |                |    |

| 6  | КО2 | РК#            | 11 |

| 3  | КО1 |                |    |

| 10 | КО0 | ПРП            | 13 |

| 19 | 0   |                |    |

| 35 | РС  | Ф <sub>б</sub> | 14 |

| 25 | ОС  |                |    |

Рис. 4

Таблица 5

| Контакт             | Обозначение    | Наименование                                 | Тип выхода         | Уровень активности |

|---------------------|----------------|----------------------------------------------|--------------------|--------------------|

| I...4               | K4...K7        | Входы первой части команды                   |                    | Лог.Ф"             |

| 5, 6,<br>8, 10      | KФ...K3        | Входы второй части команды                   |                    | Лог.Ф"             |

| 7, 9, II            | РК2...РКФ      | Входы второго разряда регистра               | Открытый коллектор |                    |

| I2, I3              | УФ3...УФ2      | Входы управления занесения и хранения флагов |                    | Лог.1"             |

| I4                  | Ф <sub>В</sub> | Выход признаков                              | Три состояния      | Лог.Ф"             |

| I5, I6              | УФФ...УФ1      | Входы управления выдачей флагов              |                    | Лог.1"             |

| I7                  | Ф              | Вход признаков                               |                    | Лог.Ф"             |

| I8                  | СРП            | Выход строба разрешения прерывания           | Обычный выход      | Лог.1"             |

| I9                  | С              | Вход синхронизации                           |                    | Лог.1"             |

| 20                  |                | Общий                                        |                    | Лог.1"             |

| 21...24,<br>37...39 | УАФ...УА6      | Входы управления РАМК                        |                    | Лог.1"             |

| 25                  | ОС             | Вход общего строба                           |                    | Лог.1"             |

| 26...29             | МАФ...МА3      | Выходы адреса колонки микрокоманды           | Три состояния      |                    |

| 30...34             | МА4...МА8      | Выходы адреса строки микрокоманды            | Три состояния      |                    |

| 35                  | РС             | Вход разрешения выдачи адреса строки         |                    | Лог.1"             |

| 36                  | ЗМ             | Вход загрузки адреса микрокоманды            |                    | Лог.1"             |

| 40                  |                | Питание                                      |                    |                    |

выдачу по линии  $\Phi_{\text{в}}$  на вход ЦПЭ или других устройств значений признаков, хранящихся в триггерах  $C$  и  $Z$ , единичного или нулевого уровня;

формирование сигнала запроса прерывания СРП при появлении на шине MA адреса, соответствующего пятнадцатой ячейке ПЗУ,

$$[(MA4-MA8)=00000, (MA0-MA3)=1111];$$

запрещение выдачи адреса строки РС.

Последние две операции используются при организации обработки прерываний в вычислительной системе.

Выполнение очередной команды вычислительной системы начинается с загрузки в ВМУ кода операции по шинам К0-К7. при этом вход загрузки адреса ЗМ=1. Сигнал ЗМ = 1 блокирует функции переходов на шинах АС0-АС6. Однако при ЗМ = 1 возможна запись и считывание РК, реализация всех функций управления признаками. По фронту синхроимпульса данные с К0-К7 загружаются в регистр микрокоманд РАМК и через выходные буферы БАС и БАК поступают в регистр адреса ЗУ микрокоманд (ЗУМК). Из ЗУМК считывается первая микрокоманда, с которой начинается выполнение данной команды. Микрокоманда содержит всю информацию, необходимую для управления вычислительной системой в данный момент времени. Микрокоманда состоит из поля микрооперации и поля адреса следующей микрокоманды. В поле адреса указывается не абсолютный адрес микрокоманды, а информация о способе определения адреса следующей микрокоманды. Эта информация из ЗУМК передается на шины УА0-УА6 ВМУ и схемой ЛСМ преобразуется в абсолютный адрес. При этом сигнал ЗМ необходимо установить равным нулю. Состояние адресных шин МА в зависимости от значения сигнала ЗМ иллюстрирует табл. 6.

Т а б л и ц а 6

| ЗМ | Адрес следующей строки |     |     |     |     | Адрес следующей колонки |     |     |     |  |

|----|------------------------|-----|-----|-----|-----|-------------------------|-----|-----|-----|--|

|    | МА8                    | МА7 | МА6 | МА5 | МА4 | МА3                     | МА2 | МА1 | МА0 |  |

| 0  | Смотри табл. 8.        |     |     |     |     |                         |     |     |     |  |

| 1  | 0                      | К3  | К2  | К1  | К0  | К7                      | К6  | К5  | К4  |  |

Одновременно с формированием адреса следующей микрокоманды происходит загрузка и чтение информации регистра признаков (флаги  $C, Z$ ). Запись информации производится по фронту синхроимпульса, а чтение при сигнале ОС=1. Если ОС=0, то  $\Phi$  находится в третьем состоянии. Функции управления входными и выходными сигналами схемы признаков задаются полем УФ0-УФ3, входящим в формат микрокоманды (табл. 7).

Таблица 7

| Группа функций             | Мономика   | Содержание функции                 | Код функций |      |      |     |

|----------------------------|------------|------------------------------------|-------------|------|------|-----|

|                            |            |                                    | УФ-3        | УФ-2 | УФ-1 | УФФ |

| Установка по входу         | <i>SCZ</i> | Установить С и Z - флаги           |             |      | 0    | 0   |

|                            | <i>STZ</i> | Установить Z - флаг                |             |      | 0    | 1   |

|                            | <i>STC</i> | Установить С - флаг                |             |      | 1    | 0   |

|                            | <i>HCZ</i> | Сохранить состояние С и Z - флагов |             |      | 1    | 1   |

| Выдача состояния по выходу | <i>FF0</i> | Выдать ЛОР "Ф"                     | 0           | 0    |      |     |

|                            | <i>FFC</i> | Выдать состояние С - флага         | 0           | 1    |      |     |

|                            | <i>FFZ</i> | Выдать состояние Z - флага         | 1           | 0    |      |     |

|                            | <i>FPI</i> | Выдать ЛОР "1"                     | 1           | 1    |      |     |

Таким образом, БМУ реализует принцип принудительной адресации микрокоманд. Однако в целях экономии оборудования возможна и естественная адресация, при которой ЗМ := 1 и вводится дополнительный счетчик микрокоманд. Переход от данной ячейки возможен не к любой ячейке ЗУ як, а лишь к определенной группе, устанавливаемой функцией перехода, действующей на лине УА. Виды переходов БМУ представлены в табл. 8.

Первые четыре перехода под действием функций *JCC*, *JZR*, *JCR* и *JCE* являются безусловными. Адрес следующей микрокоманды формируется загрузкой группы разрядов *Y<sub>i</sub>*, принадлежащих функции перехода, в выходные регистры строки или столбца с сохранением неизменными частями разрядов *M<sub>i</sub>* предыдущего адреса. Например, при переходе *JCE* адрес следующей микрокоманды будет определяться содержимым разрядов Я0-Я2, при этом значения разрядов МА0-МА3, МА8, МА7 остаются такими же, как у предыдущей микрокоманды. Кроме того, при таком виде перехода содержимое трех разрядов РК выдается на шину (РК0-РК2), что позволяет другим устройствам по необходимости принимать и использовать этот код. Остальные переходы являются условными: адрес следующей ячейки ЗУ УМК зависит от состояния триггеров флаговой логики *F*, *C*, *Z*, содержимого регистра команд РК0-РК3 или кодовой комбинации на линиях К4-К7. Например, при переходе *JCF* поле возможных адресов следующей

Таблица 8

| Обозна-<br>чение       | Назначение                                                  | Состояние управляемых<br>входов |   |    |    |    |    | Адрес следующей<br>строки |    |    | Адрес следующей<br>команды |         |

|------------------------|-------------------------------------------------------------|---------------------------------|---|----|----|----|----|---------------------------|----|----|----------------------------|---------|

|                        |                                                             | 1                               | 6 | У5 | У4 | У3 | У2 | У1                        | У0 | М4 | М5                         |         |

| <i>ICC</i>             | Переход в текущей<br>команде                                | 0                               | 0 | У4 | У3 | У2 | У1 | У0                        | М4 | У4 | У3                         | М3      |

| <i>IZR</i>             | Переход в следующую<br>строку                               | 0                               | 1 | 0  | У5 | У2 | У1 | У0                        | 0  | 0  | 0                          | М2      |

| <i>ICR</i>             | Переход в текущей<br>строке                                 | 0                               | 1 | 1  | У3 | У2 | У1 | У0                        | 0  | 0  | 0                          | М2      |

| <i>ICE<sub>1</sub></i> | Переход в текущей ко-<br>манде в группе адрес-<br>сов строк | 1                               | 1 | 0  | У2 | У1 | У0 | М8                        | М7 | М6 | М5                         | М4      |

| <i>IZL</i>             | Переход по содержимо-<br>му регистра <i>Ф</i>               | 1                               | 0 | 0  | У3 | У2 | У1 | У0                        | М8 | У3 | У2                         | У1      |

| <i>ICF</i>             | Переход по содержимо-<br>му регистра <i>С</i>               | 1                               | 0 | 1  | 0  | У2 | У1 | У0                        | М8 | М7 | М6                         | М5      |

| <i>IZP</i>             | Переход по содержимо-<br>му регистра <i>Z</i>               | 1                               | 0 | 1  | 1  | У2 | У1 | У0                        | М8 | М7 | М6                         | М5      |

| <i>IPR</i>             | Переход по содержимо-<br>му регистра команды                | 1                               | 1 | 0  | 0  | У2 | У1 | У0                        | М8 | М7 | М6                         | М5      |

| <i>IZL</i>             | Переход по левым раз-<br>рядам регистра ком-<br>анды        | 1                               | 1 | 0  | 1  | У2 | У1 | У0                        | М8 | У7 | У6                         | У5      |

| <i>IRL</i>             | Переход по правым раз-<br>рядам регистра команды            | 1                               | 1 | 1  | 1  | У1 | У0 | М8                        | М7 | 1  | У1                         | РК1 РК2 |

| <i>IPX<sub>2</sub></i> | Переход по разрядам<br>команды <i>K4</i> ≠ <i>K5</i>        | 1                               | 1 | 1  | 0  | У1 | У0 | М8                        | М7 | М6 | У1                         | РК3     |

Примечания. 1. Выдача *ЛЮ* ... *РК2* на выбранную шину.

2. Занесение информации с шин (*K4* – *K3*) в РК.

микрокоманды определяется содержимым разрядов  $YA0-YA2$  и признака С. При этом значения разрядов  $MA8$ ,  $MA7$ ,  $MA3$  по сравнению с предыдущей микрокомандой не изменяется. В зависимости от значения признака С номер колонки следующего адреса может быть при  $M3 = 1$  1011 или 1010, при  $M3 = 0$  – 0011 или 0010.

Переходы  $JPR$ ,  $JLL$ ,  $JRL$  можно использовать только в том случае, если загружен регистр команд БМУ, информация в которой поступает после выполнения перехода  $JPX$ .

В общем случае адрес следующей микрокоманды определяется разрядами, указанными в поле перехода  $YA_i$ , разрядами, сохранившимися от предыдущей команды  $M_i$ , и кодом условий ( $F$ ,  $C$ ,  $Z$ ,  $PK_i$ ,  $K_i$ ). Адрес следующей команды при  $3M = 1$  определяется из табл. 6.

Как правило, БМУ используется в качестве элемента блока центрального управления операционных устройств, обеспечивающих взаимодействие ЦПЭ, ЗУМК, оперативной памяти и периферийных устройств. Однако возможно и его автономное применение, например, в схемах контроллеров.

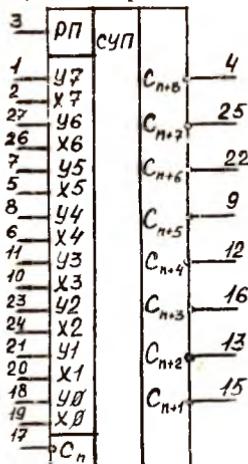

### 3. СХЕМА УСКОРЕННОГО ПЕРЕНОСА

Схема ускоренного переноса (СУП) предназначена для повышения быстродействия многоразрядного процессора, состоящего из нескольких ЦПЭ. Ее применение уменьшает длительность выполнения арифметических

Рис. 5

операций за счет одновременного формирования сигналов переноса в группе ЦПЭ. Одна схема ускоренного переноса позволяет организовать сумматор с параллельным переносом, состоящий из 8 ЦПЭ. Условные обозначения СУП приведены на рис. 5, а назначение выводов показано в табл. 9.

Каждый из элементов ЦПЭ вырабатывает на своих выходах  $X$  и  $Y$  сигналы подготовительных функций переноса, которые подаются на соответствующие входы групповых переносов  $X_i$  и  $Y_i$  СУП. СУП формирует сигналы переноса на выходах ( $C_{n+1}$  –  $C_{n+7}$ ), которые должны быть соединены с выходами СИ ЦПЭ. Выход сигнала разрешения переноса в следующую группу  $C_{n+8}$  имеет три состояния и управляется с помощью специального сигнала  $PI$ .

Таблица 9

| Контакт                                   | Обозначение                                                            | Наименование                              | Тип выхода    | Уровень активности |

|-------------------------------------------|------------------------------------------------------------------------|-------------------------------------------|---------------|--------------------|

| 1,2,5-8,<br>10,11<br>18-21,23<br>24,26,27 | X <sub>0</sub> ... X <sub>7</sub><br>Y <sub>0</sub> ... Y <sub>7</sub> | Входы групповых переносов                 |               | Лог "1"            |

| 3                                         | РП                                                                     | Вход разрешения переноса C <sub>n+8</sub> |               | Лог "0"            |

| 4                                         | C <sub>n+8</sub>                                                       | Выходы переноса                           | Три состояния | Лог "0"            |

| 9,12,13,<br>15,16,<br>22,25               | C <sub>n+1</sub> ... C <sub>n+7</sub>                                  |                                           | Два состояния |                    |

| 28                                        |                                                                        | Питание                                   |               |                    |

| 17                                        | C <sub>n</sub>                                                         | Вход переноса                             |               | Лог "0"            |

| 14                                        |                                                                        | Общий                                     |               |                    |

#### 4. МНОГОРЕЖИМНЫЙ БУФЕРНЫЙ РЕГИСТР

Многорежимный буферный регистр (МБР) является универсальным 8-разрядным регистром с выходными каскадами, имеющими три устойчивых состояния, и логикой управления, позволяющей организовать на основе МБР различные типы интерфейсных и вспомогательных устройств, например: регистры данных, мультиплексоры, двунаправленные шинные формирователи, устройства запроса прерываний и т.д.

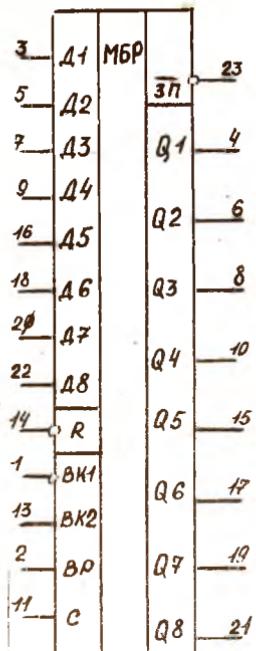

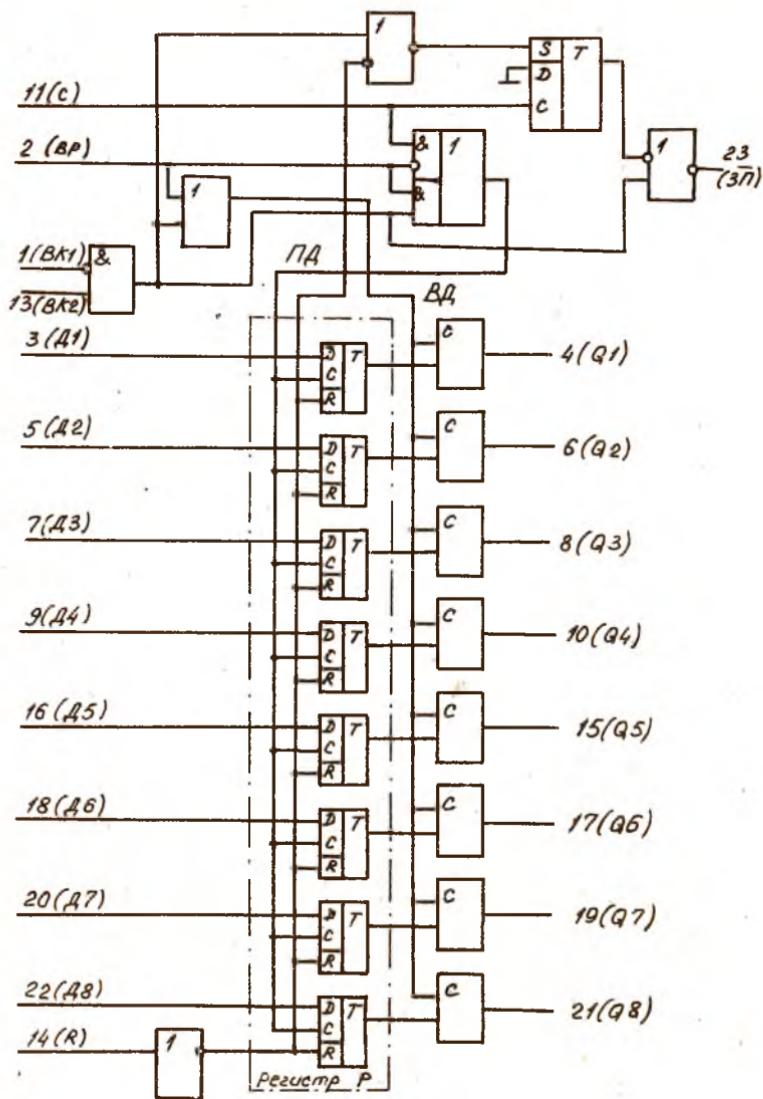

Условное обозначение МБР указано на рис. 6, а назначение выводов - в табл. 10.

Структурная схема МБР приведена на рис. 7. Информация поступает на входы  $D_1 - D_8$  регистра  $P$ , собранного на однотактных  $D$  - триггерах. Управление режимами работы МБР осуществляется с помощью сигналов, поступающих на входы BK1, BK2, BP, C.

Запись информации происходит при условии

$$PD = (BK1 \wedge BK2 \wedge BP) \vee (C \wedge \bar{BP}) = 1.$$

Выдача информации производится при  $BD = (BP \vee \bar{BK1} \wedge \bar{BK2}) = 1$ , в этом случае выходные буфера будут открыты и содержимое регистра  $P$  передается на выходные шины  $Q1 - Q8$ .

Р и с . 6

В режиме хранения информации ( $ВД = 0$ ) шины  $Q1 - Q8$  находятся в высокомом состоянии. Передача информации будет происходить в том случае, если  $ПД = ВД = 1$ .

В состав МБР входит схема, предназначенная для выработки сигналов запроса прерывания. Она состоит из триггера прерывания ТП и соответствующих логических схем. Принято, что МБР находится в состоянии прерывания, когда на выходе ЗП установлен логический ноль. Это условие обеспечивает прямое соединение выхода ЗП с входами запроса блока приоритетного прерывания, которые управляются никаким уровнем.

Сброс запроса прерывания ( $ЗП = 1$ ) осуществляется при соблюдении условия  $R\bar{V}BK_1\Lambda BK_2 = 1$ , сигнал запроса прерывания ( $ЗП = 0$ ) формируется при  $(\bar{BK_1}\bar{BK_2})VC = 1$ .

При работе в режиме записи информации, когда  $ВР = 0$ , сигнал С производит запись информации в регистр Р и установку ТП в 0.

Установка МБР в исходное состояние производится по выходу  $R$ . При этом регистр Р устанавливается в нуль, а ТП - в единицу.

Т а б л и ц а 10

| Контакт                    | Обозначение       | Наименование             | Тип выхода    | Уровень активности                       |

|----------------------------|-------------------|--------------------------|---------------|------------------------------------------|

| I.13                       | $BK_1 \dots BK_2$ | Входы выбора кристалла   |               | Лог "0" ( $BK_1$ )<br>Лог "1" ( $BK_2$ ) |

| 2                          | $BP$              | Вход выбора режима       |               |                                          |

| 3,5,7,9<br>16,18,20<br>22  | $D1 \dots D8$     | Входы информации         |               |                                          |

| 4,6,8<br>10,15,17<br>19,21 |                   | Выходы информации        | Три состояния |                                          |

| II                         | $C$               | Вход строба              |               | Лог "1"                                  |

| I2                         |                   | Общий                    |               |                                          |

| I4                         | $R$               | Вход установки нуля      |               | Лог "0"                                  |

| 23                         | $ЗП$              | Выход запроса прерывания | Два состояния |                                          |

| 24                         |                   | Питание                  |               |                                          |

Рис. 7

В соответствии с приведенными логическими выражениями для ПД, Вд и ЗП очевидны способы использования сигналов ВК1, ВК2, ВР, С, ЗП для управления МБР.

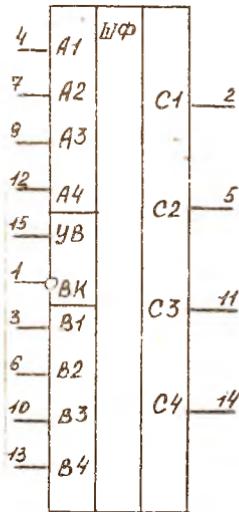

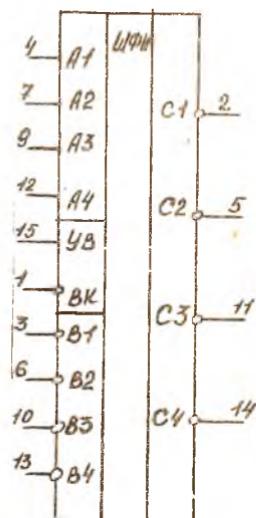

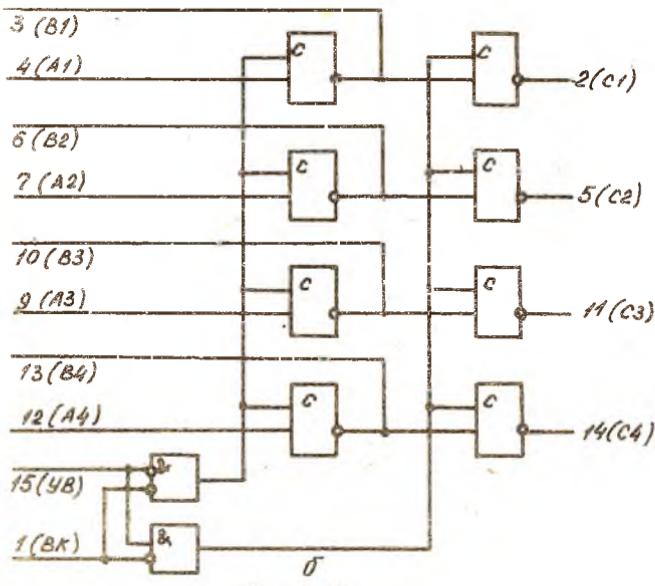

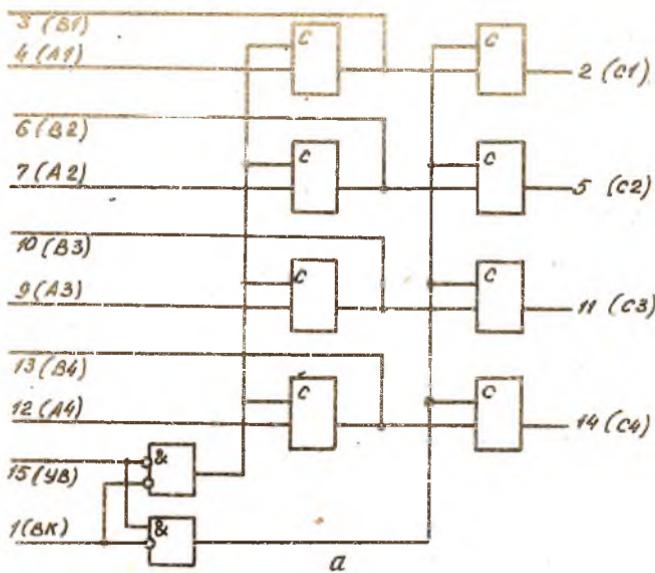

## 5. ШИННЫЕ ФОРМИРОВАТЕЛИ

Шинные формирователи (ШФ) предназначены для организации магистральной системы связи между различными устройствами. Они являются параллельными двунаправленными формирователями сигналов и представляют собой 4-канальные коммутаторы, имеющие в каждом канале одну шину только для приема информации, одну шину только для выдачи информации и одну двунаправленную шину. Выходные шины ШФ реализованы на элементах с тремя состояниями. Применение ШФ позволяет также увеличить нагрузочную способность схем, на выходе которых они применяются. В К589АН16 информация коммутируется без изменений, а в К589АН26 с инверсией. Условные обозначения ШФ приведены на рис. 8(а,б), а назначение выводов дано в табл. II. Управление режимом работы и направлением передачи в ШФ осуществляется с помощью сигналов, подаваемых на входы ВК и УВ (табл. 12).

а

б

Рис. 8

Таблица II

| Контакт         | Обозначение | Наименование                                  | Тип выхода    |         |

|-----------------|-------------|-----------------------------------------------|---------------|---------|

| I               | ВК          | Вход выборки кристалла                        |               | Лог "0" |

| 2...5<br>II, I4 | С1...С4     | Выходы информации                             | Три состояния |         |

| 3, 6<br>I0, I3  | В1...В4     | Входы /выходы реверсивной передачи информации | Три состояния |         |

| 4, 7<br>9, I2   | А1...А4     | Входы информации                              |               |         |

| 8               |             | Общий                                         |               |         |

| I5              | УВ          | Вход управления выдачей информации            |               |         |

| I6              |             | Питание                                       |               |         |

Таблица I2

| Логическое состояние по входам |    | Направление передачи  | Выходы в выключенном состоянии |

|--------------------------------|----|-----------------------|--------------------------------|

| ВК                             | УВ |                       |                                |

| 0                              | 0  | От входа А на выход В | С                              |

| 0                              | I  | От входа В на выход С | В                              |

| I                              | I  | Передача отсутствует  | С, В                           |

Структурные схемы ШФ и ШФИ приведены соответственно на рис. 9 (а,б).

## 6. БЛОК ПРИОРИТЕТНОГО ПРЕРЫВАНИЯ

Блок приоритетного прерывания (БП) предназначен для использования в многоуровневых подсистемах прерываний. Подсистемой прерываний (ПП) называют совокупность аппаратных и программных средств, обеспечивающих изменение процесса обработки информации в зависимости от определенных программируемых ситуаций.

В функции ПП входит:

инициирование прерывания от источников прерывания и формирование запросов на прерывания в соответствии с требуемым приоритетом;

определение допустимого момента прерывания и запоминание необходимой информации о прерванной программе. Выбор программы обработки прерывания и обеспечение перехода к ней;

выполнение программы обработки прерываний;

обеспечение возврата к прерванной программе.

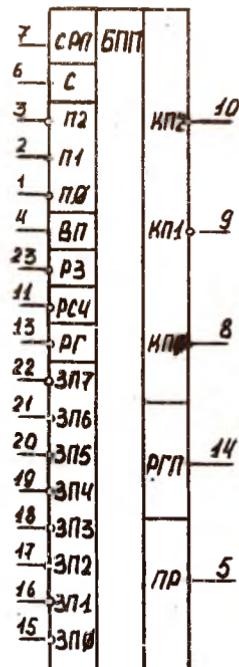

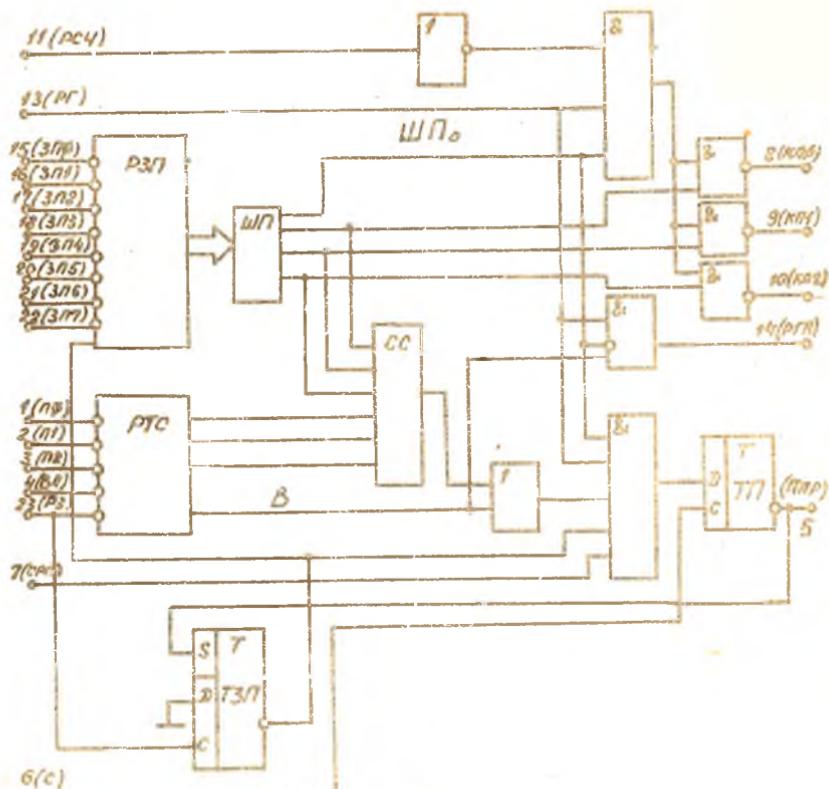

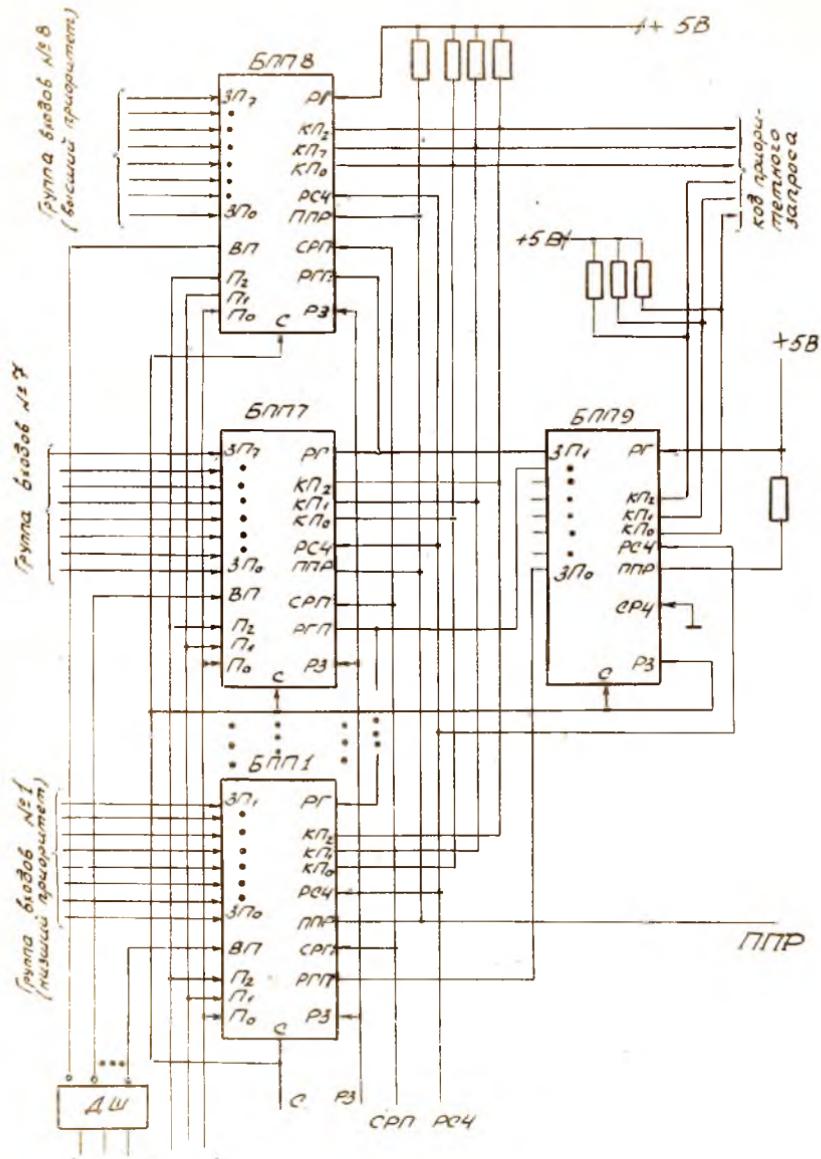

Часть этих функций реализуется с помощью БПП. Условное обозначение БПП приведено на рис. 10, структурная схема на рис. II, а назначение выводов - в табл. 13.

БПП может выполнять следующие действия:

1. Запись 8 запросов на прерывание и выбор запроса с наибольшим приоритетом.

Запросы, поступающие в произвольные моменты времени, фиксируются в регистре запросов прерывания (РЭП). Запись запросов прекращается на время нахождения триггера прерывания (ПП) в активном состоянии. Сигнал запрета записи новых запросов формирует триггер запрета прерываний (ТЭП), управляемый ПП. При одновременном поступлении сигналов по линиям (ЗП0-ЗП7) в РЭП будет записан лишь запрос с наивысшим приоритетом, а остальные запросы в РЭП не фиксируются. Наивысшим приоритетом обладает вход ЗП7, наименьшим - ЗП0.

В БПП возможно программное изменение приоритетов путем маскирования запросов прерывания. Реализация этого способа требует дополнительных аппаратных и программных средств. Например, вычислительная система может быть защищена от прерываний на период особо важной работы, если в формате микрокоманды предусмотреть специальный разряд маски, соединенный со входом ЗП7. Если в этом разряде записаны 0, то запись запросов в РЭП запрещена, при единичном значении кода блок прерывания воспринимает запросы.

2. Сравнение приоритета поступившего запроса с приоритетом выполняемой в данный момент программы и формирование кода прерывающей программы.

Рис. 10

P H C, II

TAGGART 13

| Контакт | Обозначение | Наименование                      | Тип выхода         | Уровень активности |

|---------|-------------|-----------------------------------|--------------------|--------------------|

| 1       | 2           | 3                                 | 4                  | 5                  |

| 1,2,3   | П2+П2       | Входы уровня приоритета           |                    | Лог "0"            |

| 4       | В1          | Вход выборки уровня приоритета    |                    | Лог "0"            |

| 5       | ПР          | Выход прерывания                  | Открытый коллектор | Лог "0"            |

| 6       | С           | Вход синхронизации                |                    | Лог "1"            |

| 7       | СРП         | Вход строба разрешения прерывания |                    | Лог "1"            |

Окончание табл. 13

| 1      | 2         | 3                                  | 4                  | 5       |

|--------|-----------|------------------------------------|--------------------|---------|

| 8,9,10 | КПФ + КП2 | Выходы кода прерывания             | Открытый коллектор | Лог "0" |

| II     | РСИ       | Вход разрешения считывания КП      |                    | Лог "0" |

| I2     |           | Общий                              |                    |         |

| I3     | РГ        | Вход разрешения группы прерывания  |                    | Лог "1" |

| I4     | РП1       | Выход разрешения группы прерывания | Два состояния      | Лог "1" |

| 15+22  | ЗП0-ЗП7   | Входы запроса прерывания           |                    | Лог "0" |

| 23     | Р3        | Вход разрешения записи             |                    | Лог "0" |

| 24     |           | Питание                            |                    |         |

Восьмиразрядный унитарный код Р31 преобразуется шифратором приоритета (Ш1) в позиционный код, поступающий на один вход схемы сравнения СС. Второй вход СС присоединен к выходу регистра текущего состояния (РТС), информация в который записывается при наличии сигналов выборки кристалла (ВИ) и разрешения записи (РЗ). Сигналы ВИ и РЗ формируются вычислительной системой, в которой используется БП1. Если приоритет запроса выше (код с выхода Ш1 больше кода РТС), то на выходе СС появляется единичный сигнал. Этот сигнал в дальнейшем используется при формировании сигнала подтверждения прерывания (ШР). Одновременно код с выхода Ш1 поступает на выходные вентили кода прерывания (выходы КП0-КП2), информация с которых используется вычислительной системой в процедуре обработки прерываний. Если на входах (ЗП0-ЗП7) отсутствуют запросы, то Ш1 вырабатывает сигнал "Ш1", который закрывает выходные вентили, запрещает выработку сигнала ШР и открывает вентиль, формирующий сигнал РП разрешения работы другого БП1 с более низким приоритетом. Считывание (КП0-КП3) происходит при условии  $\overline{РСЧ} \wedge Рг \wedge Ш_0 = 1$ .

3. Формирование сигнала подтверждения прерывания ШР. Этот сигнал используется вычислительной системой для организации начала процедуры обработки прерывания. Триггер прерывания устанавливается в активное состояние по фронту синхроимпульса С, если выполняются следующие условия:

- а) сигнал на выходе СС равен 1 или сигнал на входе ВИ=0. При ВИ=0 потенциал шины В равен 1;

- б) сигналы на шинах разрешения работы данной БИП (РГ), разрешения стробирования прерывания (СРП) и ТИ<sub>0</sub> равны 1;

- в) ТЗП находится в нулевом состоянии. Длительность сигнала подтверждения прерывания определяется периодом синхроимпульсов по входу С.

4. Расширение числа воспринимаемых запросов на прерывание. Систему прерывания на любое количество входов можно получить за счет увеличения числа БИП и соответствующего их соединения. Для этого в схеме БИП предусмотрены вход сигнала РГ, который обычно вырабатывается БИП с более высоким приоритетом, и выход сигнала РП разрешения работы БИП с более низким приоритетом. РП вырабатывается при выполнении следующих условий: РГ=1, код текущего состояния не соответствует данной БИП (В=1), отсутствуют запросы прерывания на входах ЗИО-ЗИ7 (ТИ<sub>0</sub>=0). Пример системы прерываний на 64 входа приведен на рис. 12. Система состоит из восьми БИП, образующих приоритетную цепочку, и БИП9, в функции которого входит кодирование номера БИП, работающего в данный момент времени. Выдаваемый в вычислительную систему код запроса прерывания имеет 6 разрядов, из которых три младших кодируют номер запроса внутри БИП, а три старших – номер работающего БИП. Высший приоритет имеет БИП8, а низший – БИП1. Три старших разряда кода текущего прерывания управляют выборкой необходимого БИП. С этой целью выходы ДШ соединены со входами ВИ соответствующего блока прерываний.

Для начала работы БИП необходимо ТИ=0 РСЧ=0, РГ=1 ВИ=1, в РТС записать код текущего приоритета. Запись производится сигналом РЗ. По фронту сигнала РЗ ТЗП сбрасывается в 0, и на РЭП приходит сигнал, разрешающий запись запросов прерывания. Сигналы запросов прерывания должны находиться на входах ЗИО-ЗИ7 до тех пор, пока ТЗП не установится в единицу. Это связано со схемой РЭП, которая реализована на триггерах типа "зашелка" (запись осуществляется при переходе сигнала из "0" в "1"). Результат анализа содержимого РЭП и РТС формируется СС и в момент прихода сигнала СРП передается на вход Д триггера ТИ. Обычно СРП вырабатывается БИУ после выполнения каждой команды. По фронту синхроимпульса С ТИ установится в состояние, соответствующее потенциалу на входе Д. Если Д=1, то ТИ переходит в единичное состояние. Сигнал подтверждения прерывания ИПР снимается с инверсного выхода ТИ и передается в вычислительную систему. Активным уровнем сигнала ИПР является "0". ИПР устанавливает ТЗП в единичное состояние, запрещая тем самым прием новых запросов в РЭП и подготавливая ТИ к сбросу в нулевое состояние (смотри состояние конъюнктора на входе  $D_{ТИ}$ ). Вто-

## Код текущего состояния

Рис. 12

рой импульс по входу С установит ТИ в нуль, что означает окончание сигнала ППР. Чтобы исключить возможность прерывания по одному и тому же запросу или запросам с меньшим приоритетом, код обрабатываемого запроса (КП0-КП3) рекомендуется записывать в РТС на время обработки прерывания.

## 7. МНОГОФУНКЦИОНАЛЬНОЕ СИНХРОНИЗИРУЮЩЕЕ УСТРОЙСТВО

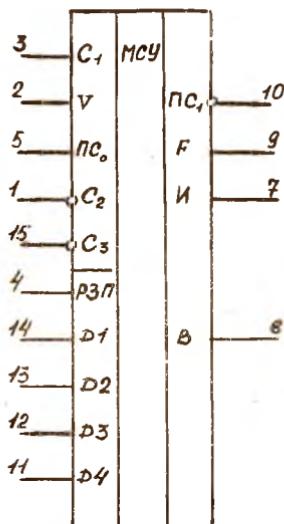

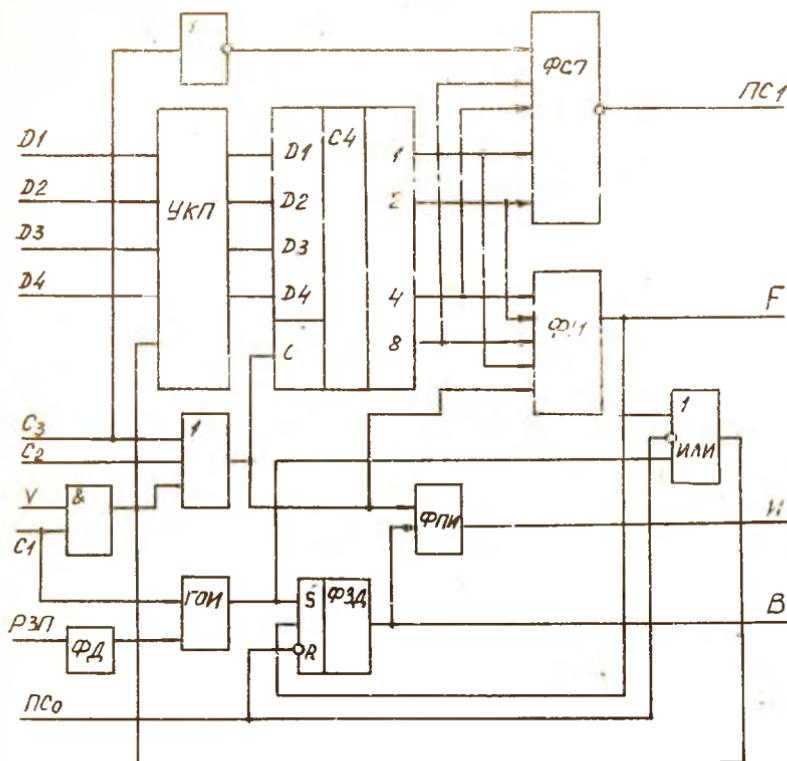

Многофункциональное синхронизирующее устройство (МСУ) выполняет функции деления частоты с переменным коэффициентом, формирования дискретной задержки импульсов, пачки импульсов с требуемым количеством импульсов, формирования импульсов заданной длительности. Условное графическое обозначение МСУ показано на рис. 13, назначения выводов

Таблица 14

Рис. 13

| Номер вывода | Обозначение | Назначение                          |

|--------------|-------------|-------------------------------------|

| 1            | $C_2$       | Вход переноса синхронизации         |

| 2            | $V$         | Вход формирователя длительности     |

| 3            | $C_1$       | Вход синхронизации                  |

| 4            | РЭП         | Вход разрешения записи              |

| 5            | $PC_0$      | Вход переноса                       |

| 6            | $B$         | Выход формирователя длительности    |

| 7            | И           | Выход формирователя пачки импульсов |

| 8            | $\perp$     | Общий                               |

| 9            | $F$         | Выход делителя                      |

| 10           | $PC_1$      | Выход переноса                      |

| 11...14      | $D4...D1$   | Входы предустановки информации      |

| 15           | $C_3$       | Вход переноса синхронизации         |

| 16           | $I_{cc}$    | Питание                             |

приведены в табл. 14, а структурная схема изображена на рис. 14. Схема содержит программируемый делитель частоты, состоящий из 4-разрядного синхронного двоичного счетчика с параллельным переносом (СЧ), схемы установки коэффициента пересчета

Рис. 14

(УКП) и специальные схемы формирователей. В состав формирователей входят генератор одиночных импульсов (ГОИ), формирователи сигнала переноса (ФСи), импульсов выходной частоты (ФИ), переменной пачки импульсов (ФПИ), импульса заданной длительности (ФЗД), входного импульса (ФД). Для увеличения разрядности можно объединить несколько схем МСУ. Для этого предназначены входы  $нC_0$ ,  $C_2$ ,  $C_3$  и выход  $нC_1$ . При использовании одной микросхемы на входы  $нC_0$ ,  $C_2$ ,  $C_3$  подается ноль.

В исходное состояние схема устанавливается подачей на вход  $нC_1$  импульса произвольной длительности. ФД формирует сигнал стандартной длительности, который подготавливает ГОИ для приема одного импульса тактовой частоты со входа С1.

деление частоты выполняет СЧ, на выходе  $F$  которого с помощью ФИ импульсы появляются каждый раз, когда все разряды устанавливаются в единицу. На вход СИ подаются импульсы тактовой частоты, а на вход  $V$  — сигнал разрешения положительной полярности. Предварительная установка СЧ осуществляется подачей соответствующих кодов со входов Д1-Д4 через УКИ в момент появления импульса на выходе схемы ИЛИ. Код пересчета, который необходимо подать на входы Д1-Д4 для получения нужного коэффициента деления, определяется как  $K_n = 2^n - K_g$ , где  $n$  — число разрядов устройства;

$K_g$  — коэффициент деления устройства,

$K_n$  — код пересчета (десятичный эквивалент);

$$K_g = 2^n - K_n.$$

Например, для деления частоты в 7 раз с помощью одного МСУ  $K_g = 7$ ,  $n = 4$ ,  $K_n = 9$ , т.е.  $D_1 D_2 D_3 D_4 = 1001$ .

В режиме формирования длительности импульса выход В необходимо соединить со входом  $V$ . На вход РЭП подается импульс начальной установки. Первый импульс тактовой частоты  $f$ , подаваемой на вход СИ, переводит с помощью ГОИ и УКИ счетчик в состояние, соответствующее коду пересчета на входах Д1-Д4. Одновременно триггер Ф3Д устанавливается в единицу и разрешает прохождение частоты  $f$  на вход СЧ. Счетчик ведет отсчет импульсов до состояния, когда все триггеры устанавливаются в единицу. При этом на выходе ФИ появляется импульс, устанавливаемый Ф3Д в нулевое положение. На выходе В формируется положительный импульс, длительность которого определяется кодом пересчета:

$$t_H = \frac{2^n - K_n}{f} + \tau_H,$$

где  $f$  — тактовая частота;

$t_H$  — длительность импульсов частотой  $f$ .

При формировании пачки импульсов режим работы МСУ аналогичен предыдущему. Сигнал с выхода Ф3Д поступает одновременно на один из выходов ФИ, на другой вход поступает тактовая частота со входа СИ. Число импульсов в пачке, формируемой на выходе  $U$  ФИ, определяется длительностью положительного потенциала на выходе В Ф3Д, т.е. кодом пересчета на входах Д1-Д4.

$$\text{Число импульсов в пачке } N = 2^n + 1 - K_n.$$

Для реализации режима дискретной задержки необходимо соединить выход  $V_1$  со входом  $V_1$ . Импульс на выходе  $F$  появляется через определенное число тактов частоты  $f$  после прихода сигнала  $V_{31}$ . Задержка сигнала на выходе по отношению к сигналу, поступающему на вход  $C_4$ , определяется кодом пересчета на входах  $D_1-D_4$ . Время задержки

$$t_3 = \frac{2^n - K_n}{f} + \tau_n .$$

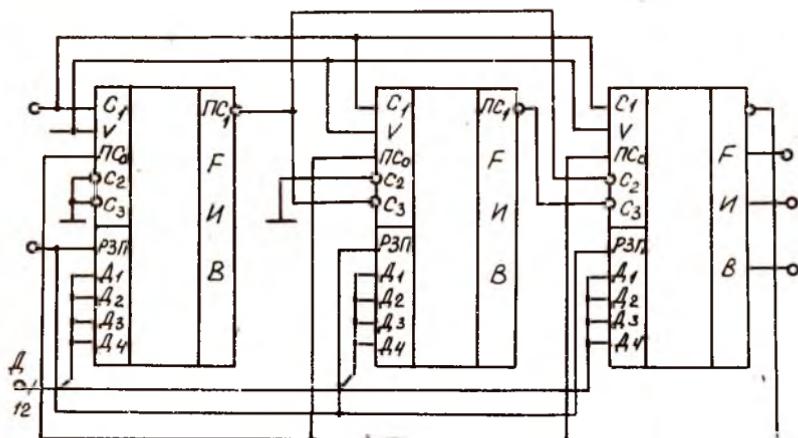

Организация многоразрядного МСУ показана на рис. 15.

Рис. 15

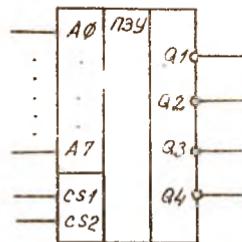

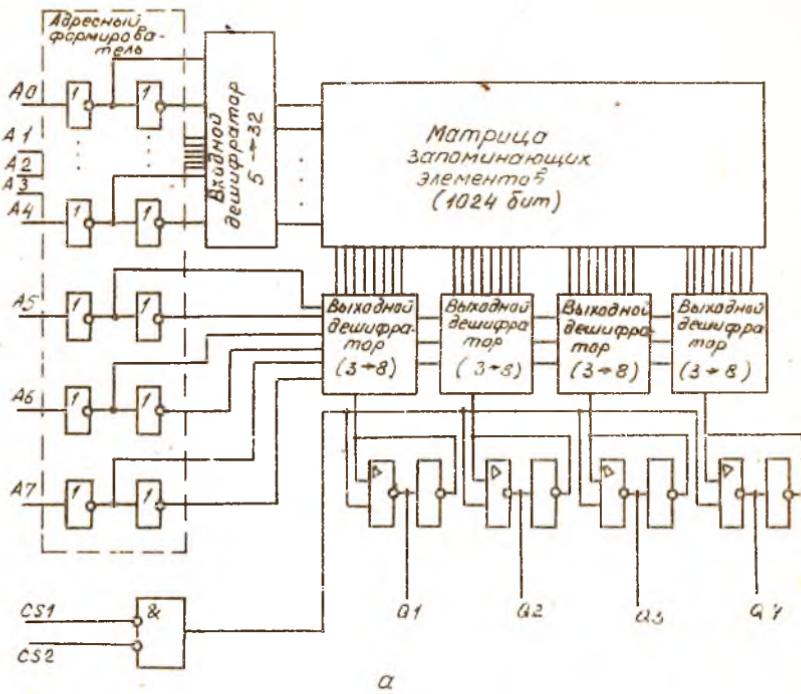

#### 8. ПРОГРАММИРУЕМОЕ ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (ПЗУ)

Запоминающее устройство (K556PT4) представляет собой БИС ТТЛ типа с диодами Шотки и выполнено методом планарно-эпитаксиальной технологии, структурная схема приведена на рис. 16,а. Запись информации в ПЗУ производится пользователем путем пережигания никромовых перемычек импульсом тока один раз во время эксплуатации схемы. Считывание информации происходит при подаче 0 на оба входа  $CS$ . При любой другой комбинации сигналов на этих входах на выходах ПЗУ имеем единичный потенциал. Считывание информации происходит путем подачи кода

Рис. 16

адреса на входы A0-A7 с выхода  $Q1 - Q4$ . Выходы усилителей считывания выполнены по схеме с открытым коллектором. Входы разрешения выборки CS обеспечивают возможность выбора схемы при объединении ППЗУ в большие массивы.

До программирования в микросхеме по всем адресам и разрядам записаны нули.

Условное обозначение ППЗУ приведено на рис. I6,б.

ППЗУ K556PT5 имеет аналогичную структуру и организацию (512x8).

В качестве ППЗУ могут использоваться микросхемы других серий, отвечающие необходимым требованиям по быстродействию (например, I33, I55, и т.д.).

#### Л и т е р а т у р а

1. Березенко А.И., Корягин Л.Н., Назарьян А.Р. Микропроцессорные комплексы повышенного быстродействия. - М.: Радио и связь, 1981.

2. Балашов Е.П., Пузанков Д.В. Микропроцессоры и микропроцессорные системы. - М.: Радио и связь, 1981.

3. Каган Б.М., Сташин В.В. Микропроцессоры в цифровых системах. - М.: Энергия, 1979.

## С о д е р ж а н и е

|                                                                     |    |

|---------------------------------------------------------------------|----|

| • Технические характеристики<br>микропроцессорного набора К589..... | 3  |

| 1. Центральный процессорный элемент (ЦПЭ).....                      | 4  |

| 2. Блок микропрограммного управления.....                           | 13 |

| 3. Схема ускоренного переноса.....                                  | 20 |

| 4. Многорежимный буферный регистр.....                              | 21 |

| 5. Шинные формирователи.....                                        | 24 |

| 6. Блок приоритетного прерывания.....                               | 26 |

| 7. Многофункциональное синхронизирующее устройство                  | 32 |

| 8. Программируемое постоянное запоминающее устройст-<br>во.....     | 35 |

| Л и т е р а т у р а .....                                           | 39 |

Составитель – Владислав Германович Иоффе

МИКРОПРОЦЕССОРНЫЙ КОМПЛЕКТ К589

Редактор Е.Д.Антонова

Техн.редактор Н.М.Каленюк

Корректор М.В.Павлова

Подписано в печать 22.12.84.

Формат 60x84 1/16. Бумага оберточная белая.

Печать оперативная. Усл.п.л. 2,32. Уч.-изд.л. 2,0.

Т. 500 экз. Заказ 1024 Бесплатно.

Куйбышевский ордена Трудового Красного Знамени

авиационный институт имени академика С.П.Королева,

г. Куйбышев, ул. Молодогвардейская, 151.

Областная тип.им. В.П.Мяги, г.Куйбышев, ул.Венцека, 60.